在课题组这儿画了好几块PCB了,感觉使用Candence画板这活完全就是经验性的工作。学习曲线陡峭,简直就是个阶跃函数,掌握了基础之后就是不断在实际操作中熟练技巧(为什么你这么熟练啊…)。画原理图的时候如果没有以前的参考还会相对复杂一点,要对照datasheet按照要求来连接逻辑关系,布PCB简直就是堆工作量了,经常陷入长时间布线停不下来,总想多做一些早点搞完,但是实际上已经累得头晕脑胀的毫无效率了(珍爱生命远离画板…)。

虽然这么说但是过程中需要注意的地方也挺多的,这里把自己以前学习的小记和操作过程的思考记录下来,以后操作前先复习一下以免多次无意义的工作(没错 就是经常删了重布 删了重布)。

基本概念

Cadence提供了两个集成的、从前端到后端的设计结局方案:Concept-HDL到Allegro;Capture到Allegro。

Capture CIS区别于Capture的地方在于CIS——Component Information System,该模块可对元器件和库实施高效管理,还可通过Internet Component Assistant查阅添加元器件。(不过我基本上没用过,都是自己保存的元件库,这个还需注意吧)

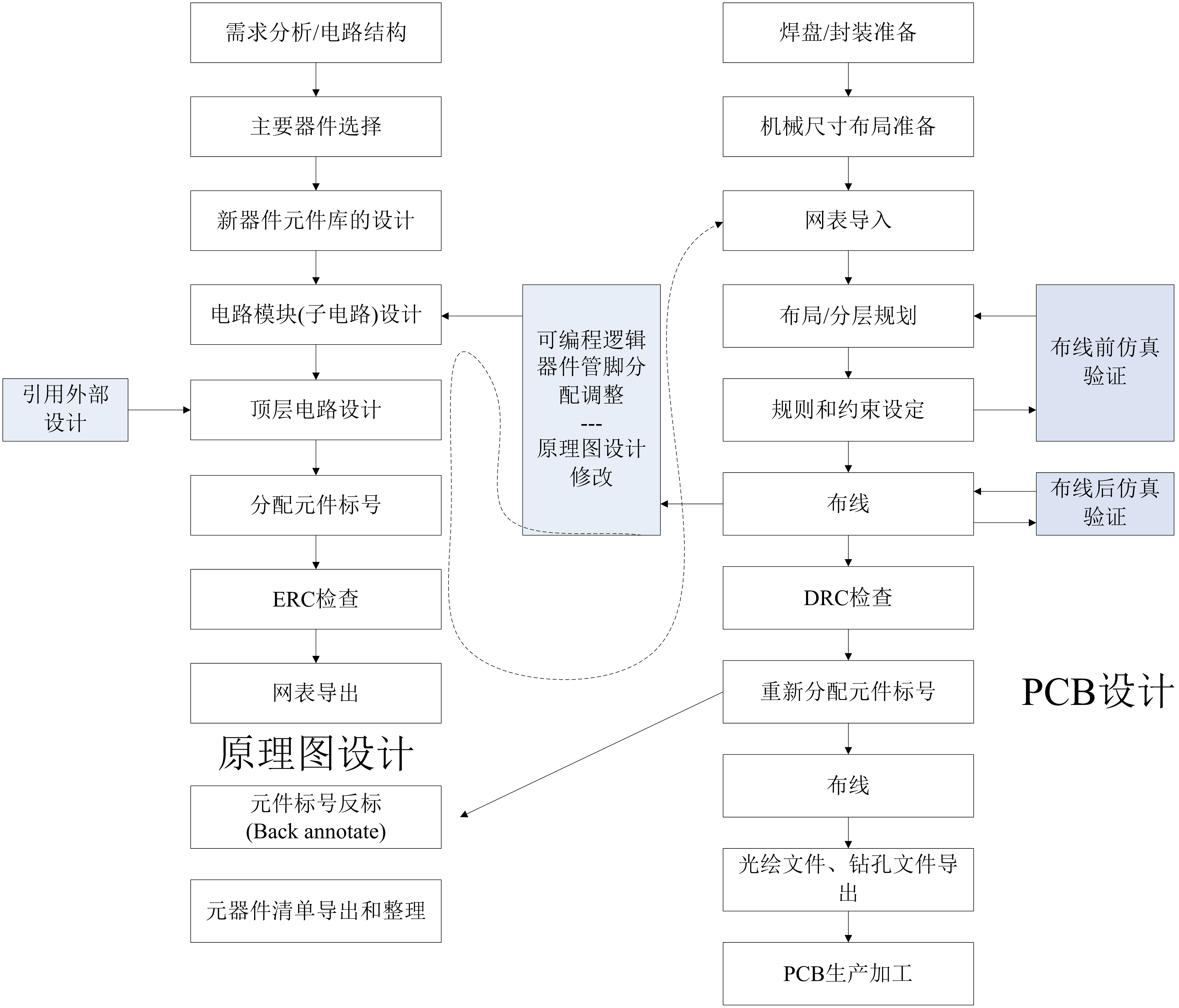

设计总体思路:

- 原理图:根据框图,确定元器件,若库里无相应器件,需自己画器件模型;再连接元器件之间的端口。首先确定各个模块(每一个文件夹就对应一个模块Schematic Design—Schematic Folder—Schematic Page),在模块内各page连线,再在TOP层将各个模块连接起来。

- PCB:根据原理图确定下来的连接关系,对元器件进行具体的布局布线。首先确定板卡的尺寸、固定孔,然后布局(根据具体需求和指导原则),接着布线,最后检查其合理性,对不足的地方修改

或者推翻重来。

原理图设计

元件库制作

注意事项

- 如果在参考项目中有需要修改的package,点击该元器件—Edit Part—View Package—save as选择自己的元件库保存。

- 如果已有的库里没有元件对应的package,可上官网找CAD文件用官方软件转换为.olb,复制到自己的库中。如果没有,按照管脚定义列表excel自己画。Excel也找不到就自己画吧。

- 元件会有多种封装,不同封装管脚排列不同,如AD9236有RU-28和CP-32-2两种,分别对应尾缀:BRU和BCP。一般在芯片手册的Order Information或Ordering guide中会包含完整的尾缀和封装对应关系。

- 元件库名称必须带有表示元件封装的尾缀信息

- 为实现后续功能,元件库管脚类型(type)必须与实际元件一致

常用的管脚类型有:Input, Output,3state,Bidirectional,Open Collector,Open Emitter,Passive,Power等 - 同一功能有多个管脚,在管脚功能后用不同数字区分(如VCC1,VCC2,GND1,GND2);数字命名在管脚数较小时按照递增编号;管脚数较多时,可用管脚号(如VCCINT56表示该电源管脚在第56号管脚上)

- 一般应将管脚按照功能分组摆放

- 元件管脚必须置于编辑界面的网格(grid)上,否则画原理图时会出现连接错误。

制作元件

- 新建元器件:New library-new part。

- 放置引脚:

单个引脚Place Pin:其中Number管脚号是非常重要的属性,在PCB设计中,使用Number属性与封装的PinNumber对应,从而建立原理图与PCB的联系。管脚号不光可以是数字,也可以是字母,或字母数字的组合(如某些BGA封装)的管脚号就是字母数字组合。但必须和封装上的管脚号一一对应。

多个引脚Place Pin Array—>edit Properties。调整顺序,沿虚线框画矩形外框。

在制作FPGA等引脚非常多的元件时,官网会有相关文件方便制作。 - 绘制外形:Place-Line or Rectangle。

绘制完成后保存至相应的.olb中。

另一种方法:new part from spreadsheet,按照datasheet填写表格,其中No. of Section用于表示元件中的第几个part(在multipule-part package情况下)。

概念对比

Package包装:即库中一个完整的元件,一个Package一般对应PCB中一个元件的封装(Footprint)。

Part部件:组成一个完整元件的一个或多个部分。某些元件内部可以按照功能划分为多个部分,每一部分占用元件的一部分管脚。

Single Part:元件由唯一的Part组成,大多数简单器件。

Multipule Part Package:

- Homogeneous:内部各Part功能和符号完全相同的元件。每个Part的图形和管脚数和功能都是相同的,但管脚号可以不同。并且可以有部分重复的管脚(如74LS14每个Part上均有VCC和GND两个管脚,不过这些重复的管脚应该都是对应的实际上同一个管脚)。不能使用[New Part From Spreadsheet]制作。

- Heterogeneous:元件由多个不同的Part组成。不允许同一个管脚在不同Part中出现(软件不会报错)。

原理图层次

一个原理图design包含多个模块Block(有一个root schematic即顶层模块),而模块由多个Page组成。

Block上的端口(Port)来自于图中各Page上放置的Port符号。如果把Block也看成一个芯片,则Port是这些芯片的管脚。

Off Page Connector的作用是连接同一个图中不同页(page)的电路。而Net alias用于连接同一个Page内的电路。

电源端口是全局的。

原理图制作

新建项目

New-Project。在circuit文件夹下创建sch和pcb分别存放原理图和pcb设计。

修改模板

包括Title Block和Page Size: [Option]-[Design Template]- Title Block-Symbol。

New symbol可创建特殊元件,如TitleBlock、电源、地、port、off-page connecter;改变图纸大小Schematic Page Properties-Page Size一般选B及以下。

创建顶层页面

Root Design中分别建立Page1: Title、Page2: Topology和Page3: Top三个页,在Topology页中绘制或粘贴电路框图。

添加库

[Place]–[Part]中添加自己的元件库以。注意“Design Cache”并不是一个真正的库文件,而是当前工程的设计缓冲。

分模块画子图

[New Schmatic]-[New Page]创建子图。然后放置元件,重点检查元件标号(Part Reference)和封装(PCB Footprint),修改value。快捷键H,V,R可分别左右、上下调换元件和旋转元件。

放置电源、GND符号,端口符号等,然后wire连接逻辑关系。

指定net alias

一般与端口相连的网络名称应与端口名称相同。网络标号只在Page内起作用,因此不同Page中的网络标号是可以相同的。

在顶层图中放置子模块

[Place]-[Hierarchical Block]。缺省情况下,所有的输入都在左边,所有的输出都在右边,可以根据绘图需要进行调整。

若修改了Page中的设计,如使用Place H pin增加、减少了Port,可以在Block处使用[Synchronize Up]命令,更新Block。如果在Block上增加了Port或减少了Port,则可以使用[Synchronize Down]。

原理图复用

一个Schematic作为一个Block在顶层中可以复用。

原始的属性所代表的元件,称为Instance,对应属性页中的白色一列;而由于复用新增的两列所代表的多个同类元件,称为Occurrences,对应属性页中的黄色列。在存在复用的设计中,Occurrences中的属性(可不同),才是真正使用的属性(在导出PCB网表时使用)。

电路模块级的重用

可将一整个已有的电路设计复用,原理图对应相应的.dsn,PCB布局对应相应的.mdd(需要在PCB中添加至Module Path中)。其中可重用DSN原理图中的元件经过特殊处理,具有Reused ID属性。若被外部引用的DSN名为DsnName;而DSN中被引用的schematic名称为SchName,则对应的MDD文件名称应为DsnName_SchName.MDD。在PCB设计时,.dsn和.mdd通过文件名来匹配。

[Place]-[Hierarchical Block]-[Browse…]找到复制过来的xx.dsn(设置文件名才能与PCB中的.mdd匹配)。

在[Browse]选择文件后,Path and filename中为DSN文件的完整路径,为保证整个Sch目录复制到别的机器或目录还能改正确打开原理图,必须将其改为相对路径。

分配元件标号

选中.dsn—annotate。注意Action中Unconditional reference update一般不使用,另Reset reference numbers to begin at 1 in each page也绝对不能选中,会导致标号重复。

第一步:将页面中的标号都置为“?”。Scope选Update entire design,Action选Reset intersheet References,Mode选Preferred,选中Include non-primitive parts(即将Block也标号),确定即可。

第二步:若没有使用外部重用模块(.dsn .mdd),则Action选中Incremental reference update确定即可。若使用了外部重用模块,则在Allegro Reuse中标号。

DRC电气规则检查

DRC检查管脚连接冲突、总线宽度匹配,短路(同一个元件管脚上有多个网络名)等原理图设计中潜在的错误。检查范围有限,可能误报,需谨慎仔细查看。

Edit—browse—DRC Markers可查看检查出的错误。

网表导出netlisting

在导出网表之前必须将所有元件的PCB Footprint属性填好(如果某些元件的封装还没有画,也要先填一个名字)。

Tools—create netlist,在PCB editor页面选中Create or Update Allegro PCB Editor Board,若是修改了原理图更新PCB,则要选择input board。Place changed需要注意下。

一定要注意在打开的PCB中另存至pcb文件夹中!!!这是血泪的教训啊!!!不然再次导出是要被覆盖的啊!!!

注意:导出时若遇到ERROR(ORCAP-36004),是对多part元件编辑时,软件会自动给编辑的part添加尾缀造成多part不一致,在Edit part页面选择Options-Package properties删掉尾缀。若是有多次编辑,则会提示错误封装名重复。这时进Design Cache将相应的封装用自己的库替换掉。注意以后要避免直接修改Part封装导致这种错误,而要在库中修改再替换。

注意:可以使用edit—browse—选择相应的器件进行修改。比如修改part的footprint,就可以进入part,选择需要修改的元件,ctrl+E修改属性里的footprint。修改port、net的名称也可以这样做。

也可以Ctrl+F查找器件,如查找所有电阻,则在查找选项里选中parts,然后搜索R*,即可选中所有的电阻进而修改footprint。

也可以直接选中一页或.dsn,右键选择edit object properties。

PCB设计

备注:1 mil=1 inch/1000=25.4mm/1000

1 mm=39.37…mil≈40mil

制作焊盘

Pad Designer-Parameter中,type焊盘类型有:Through通孔、Blind盲孔、single单层,其他参数自己看看吧。

Layer中,需要定义每层的参数。一般需要定义的信号层有Begin Layer、Default Internal、End layer(对于过孔来说就这三个层就足够了,中间层都会用Default internal的参数自动匹配),另外非信号层一般还需要定义:Soldermask_top、Soldermask_bottom(阻焊)。在设计PCB时,阻焊层(Soldermask_top和Soldermask_bottom)是反向显示的,即不涂阻焊材料的地方是一个填充的图形,覆盖阻焊的地方没有图形。PCB上一般只有焊盘上不会覆盖阻焊材料,其它的连线、铺铜都被阻焊材料覆盖。一般直径要多设10mil。

Regular Pad是通常意义下的焊盘,大小根据datasheet设定,一般焊盘宽度应该大于至少等于管脚宽度,焊盘长度两倍于管脚长度使之对准中心(焊盘间距5mil以上没问题);Thermal Relief是焊盘要与周围敷铜连接时的状态,若焊盘和周围铺铜的网络相同,会自动用4或8条将焊盘与周围铺铜连接,周围铺铜与焊盘边缘隔开的距离是Regular的半径和Thermal Relief半径之差,建议直径多设12mil;Anti Pad是焊盘与周围的铺铜网络不同(因该绝缘开)时隔离的形式。

总结下来涉及到的数据有:

Drill diameter 按需

Regular Pad 按datasheet,焊盘宽度大于等于管脚宽度最大值,焊盘长度两倍于管脚长度中间值

Thermarl Relief 大12~16mil (0.3~0.4mm)

Anti pad 大12~16mil (0.3~0.4mm)

Soldermask 直径大regular pad 8~10mil,长宽都大8~10mil (0.2~0.25mm)

制作封装package symbol

用封装来表示元件管脚、物理尺寸以及管脚位置等信息。不同的元件如电阻、电容可能会用相同的封装,如0402、0603。

PCB封装只代表器件的尺寸大小等物理特性,封装上的管脚本身没有任何电气属性;而原理图符号是一个器件电气上的抽象表示,代表着器件管脚的输入、输出等电气属性,但符号本身不包含尺寸、管脚位置等物理特性。

原理图中符号通过PCB Footprint属性与PCB封装库中的同名封装对应;原理图符号上的管脚与封装的对应焊盘对应(管脚号与焊盘号对应).

一个package symbol与两个文件对应:.dra文件可编辑;.psm不可编辑,由.dra生成,需添加至psmpath。

Allegro中有很多对象都叫symbol,如Mechanical Symbol(机械符号)、Format symbol(图纸格式符号),Shape symbol(形状符号,画异型焊盘时能用到),以及Flash symbol(在焊盘设计中用来确定特殊形状的Thermal和anti Pad)。这些符号设计阶段都是*.dra文件,然后生成对应的symbol文件,但扩展名是xxm(xx是其它字母)。在PCB设计时,如果要使用这些symbol,都须要把xxm所在目录加入design_path中。

注意几个概念:

Ref Des–reference designation元件标号在Silk Screen层,如U,R,C*等;

封装占用面积,用Place_Bound_Top画一个封闭区域(Shape)来表示;

Package Geometry封装轮廓在Silk Screen层,生产时与Ref Des的Silk Screen合并成一个光绘文件,用于在PCB表面印字。

具体步骤

- 模板向导

[File]-[New]- Package symbol(wizard)——选择类型、模板——

确定管脚数(N),管脚间距(e)必须精确,焊盘中心距离(e1)取偏大(就最大宽度),封装外形丝印的宽度(E)取最小、高度(D)取最大——选择焊盘padstack——选择参考坐标symbol origin,并选中Do not create a compiled symbol在后续创建。 - 修改封装

调整grid以便编辑——添加1管脚标注:选择圆形Shape–Option页选择Active Class and Subclass为“Package Geometry和silk_screen_Top—选择圆心在管脚1右边—命令行ix 0.5(单位mm)确定半径。 - 生成符号文件.psm

[File]-[Create Symbol]生成PCB设计使用的Symbol文件。一般将所有封装的Symbol文件都放在一个目录下以备使用。

注意

封装符合要求的条件:合适的焊盘大小;精确的焊盘间距;Component—Ref Des—Silkscreen 层元件标号前缀;Package Geometry— Silkscreen层元件外形轮廓; Package Geometry—Silkscreen层绘制极性方向、1管脚方位;[Setup]-[Aereas]-[Package Boundary]定义元件实际PCB面积。(用向导绘制基本上已经概括完了)

Package Geometry的Silkscree_Top以及Component—Ref Des元件标号中的Silkscreen_Top在后续处理中会作为PCB顶层丝印的一部分;

Commond命令:

x 10 20 : 将鼠标定位在绝对坐标 (10,20)处

x 20 : 不改变上一次鼠标点击的y坐标,将x坐标定位在x坐标为20处

y 30: 不改变上次点击的x坐标,将y坐标定位在30

ix 10 20:相对于上次点击的位置,x向右移动10,y向上移动20

ix -10:相对于上次点击的位置,x向左移动10

iy 10:相对于上次点击的位置,y向上移动10

制作机械符号(画外框)

PCB机械符号包括:

- PCB的外形、尺寸要求;

- PCB的安装固定要求;

- 系统中其它部件在PCB上安装固定的要求,抗冲击的PCB上的金属加强结构

- PCB上禁止布线、和放置元件的区域(或允许布线、放置元件的区域)

- PCB上接插件放置的位置

- PCB在制造过程中切割、倒角等要求等

需要制作Mechanical Symbol的场景:完全自由设计,比如设计一个实验板,可以自由定义板子的外形、尺寸等。这种情况不用设计专门的Mechanical Symbol,只需在PCB设计环境用Board Geometry用line画一个框即可定义电路板的外形。

不需要制作Mechanical Symbol的场景:多种PCB使用同样的机械定义,如同一种形式的板子会设计很多种;由业界标准定义的PCB,如PCI板卡、VME、CPCI板卡等;设计好后可以反复利用。

下述的处理不管在需要制作Mechanical Symbol的场景,或是直接在工程中画外框的场景都会用到:

- 设置图纸大小:[Setup]-[Design Parameter]-[Design],设置单位和Extents,确定原点和宽高。

- 画PCB外框:选择[Add]-[Line]菜单,再选择右侧属性页中的子类为Board Geometry–Outline;根据尺寸输入命令确定外框。注意画外框时要一条边一条边地画,否则后面倒角不能选择segment。

- 倒角:[Manufacture]-[Drafting]-[Chamfer]命令,在右侧的Option窗口输入Trim Segments和Chamfer angle为:First2;Second0;Chamfer angle45;若是倒圆角则选择Fillet。

- 安装孔:Add Circle、Add Line。画好一个孔后,使用复制功能,并iy/ix至相应位置。

- 添加尺寸标注:[Manufacture]-[Dimension Environment],右键选择Parameter设置单位,右键选择需要的标注项进行尺寸标注。

画图前的设置

层叠结构Cross Section

[Setup]-[Cross-section]:添加层的属性,Layer Type中Conductor为通常用于走信号线的层、Plane为平面用于电源或地(平面即整一层铺铜均属同一个网络,有时一个平面可分割成多个区域用于不同的电源或地,注意需保证其较大面积和低阻抗连接路径)。

常用的层叠结构有:双面板TOP BOTTOM;四层板TOP GND1 PWR1 BOTTOM;六层板TOP GND1 SIG1 SIG2 PWR1 BOTTOM;八层板TOP GND1 SIG1 PWR1 GND2 SIG2 PWR2 BOTTOM。

设置工作路径Design Path

[Setup]-[User Preferences]-[Design Path]:module path为复用MDD文件路径;PAD Path为焊盘路径;Psm Path要设置用到的所有symbol的路径,包括packages symbol(psm–pcbsymb),mechanical symbol(bsm–pcbMechSymb),以及pcbFlashSymb,PadShapes;

添加过孔:Constraints-Physical-All layers选择Vias添加需要用的过孔。

设置图纸大小、单位、边框、颜色

参考上小节制作机械符号。

颜色可使用已有的script。另一种方法:在已有板子的基础上且层叠结构的名字一致,可export-parameter选中color相关参数,再在需导入brd中import-parameter。

设置快捷键

Command中键入echo $localenv找到env文件的路径。打开env(没有就自己创建),在一堆#前输入快捷键命令。如alias ~E move(注意这里要大写),funckey w add connect。注意alias命名的可在Command输入但不能设置单键,而funckey则可以设置单键。

可在Tools-Utilities中查看支持的键盘命令以及已有的快捷键。

敷铜

Shape–Polygon敷铜(可Edit—Z-copy复制平面到另一层)。

方法一:敷铜前可以先选择相应的电源/地net高亮,然后再在Shape中选择net画形状,注意拐角取45度。

方法二:先画好一整块敷铜,再Anti Etch分割平面。

Shape—Edit Boundary可任意更改敷铜的边界。注意敷铜与过孔的连接可在Shape—Global Dynamic Params中修改,热风焊盘Thermal relief connects中连接方式一般Full connect或Orthogonal正交。

需要在敷铜中间挖空时,选择Shape—Manual Void。

不同电源信号的敷铜间隔最小可至0.2~0.3mm。

布局

PCB中灰绿色的连线叫做(Rats),表示需要连接而还未连接的网络;

[Place]-[Quick Place]:可将剩余的所有元件都暂时放到PCB中,再慢慢摆位置;

可通过与原理图互动来选择元器件。这样可以根据信号的流向来逐个放置元件,有利于边放置边检查电路原理图,同时也利于根据元件的功能来考虑放置位置。

布线

可在[Display]-[Show Rats]-[Components]选择显示相应器件的飞线。

走线宽度一般不小于6mil(0.1524mm),线间距以3W原则即:走线中心之间距离至少为线宽的三倍,这样可使走线在另一走线的70%磁通量边界范围外,若要到98%,线间距需大10倍线宽。

差分线的线宽和线距理论上是用工具计算的(SI9000),但是没用过…目前用过的线距/线宽有8/4.5、6/4 mil。

注意绕线的时候,一般选择3x space。

差分线

在Setup-Constrains-Constrains Manager中的Electrical-ECS设置布线规则,重点在等长(Static Phase),视具体情况可设为5mil(0.127mm);然后在Net中为差分对绑定相应的规则。

总线做等长约束在Relative Propagation Delay中Create Match Group再定义约束参数。注意参数中的Delta:Tolerance,Delta指需要设置的值与Target的差值,设为0即可;Tolerance指可容忍的延迟差值,按需要设为0.2~0.3mm或者更大。

在Physical中设定宽度(Line Width)等参数;

在Spacing中为差分对设定对与对之间的间隔(Line to All),似乎在Ecs和Pcs中设定的Gap优先级更高,这里设定Line to line应该只对差分对之间起作用。注意!在ECS中要设置Min Line Spacing的值,否则会提示间距错误的DRC。

设定差分对时进入Auto Setup设置后缀后可自动设置。

注意在Setup-Constrains-Mode中将需要检查的DRC打开,否则不会显示。

扇出

Fanout,在焊盘引脚附近打孔再连接线。可在Route-PCB router-fanout by pick选择symbol自动扇出,右键Setup可进行相关设置。若对连线有要求可先在Constrains manager中修改默认走线宽度。

Xnet

约束走线等长时,会遇到一个电阻/电容连接的两根线看做同一条net来约束长度的情况,此时需要将这个电阻两端的net组合为Xnet。

方法:Analyze—Model Assigment—选择需要设置的电阻/电容—进入设置页面选择对应管脚—Ok。然后再在约束管理器中选择Xnet约束等长。

制板

光绘文件和钻孔文件;

说明所制作PCB的厚度,各层的重叠顺序(如对PCB上走线的阻抗等有特殊要求,一般应指出层叠结构、介质类型);

明确最小线宽、最小线距、最小钻孔等加工工艺;

复用模块

- 在原理图中,选择根项目 Annotate-PCB Editor Reuse,选择Generate Reuse module并确定后,选择原理图中所有器件右键Edit Properties,能看到每个器件有唯一的Reuse ID属性,说明复用模块生成成功。

- 从原理图生成PCB布局布线完成后,选择Tools-Create Module,框住所有器件并选择原点,另存为mdd复用模块,注意名字必须是原理图项目名_根page名的级联。

- 在需要用复用模块的原理图中,新建Hierarchical Block,Implementation Type选择Schematic View,Path选择复用模块.dsn,Implementation name选择复用模块Page名称。摆放完成后,在Tools-Annotate中选择PCB Editor Reuse,Function中选择Renumber design for reuse module,并在对下方选择好复用模块,这样就完成了复用模块在工程中的标号。生成PCB后在Place-Manually中选择Module Instance摆放至相应位置即可。

经验

电源

在电源之间转换时,会用电感用于两种不同电源之间的滤波。

电源芯片根据所连接芯片的功率(电流)进行选择,同时考虑效率、纹波、封装等因素。

使用LDO(Low Drop Out)电源芯片时,注意Dropout voltage的值,输入一般不能等于输出电压,需更高。

电源芯片对滤波要求较高,datasheet中一般会有layout建议,如滤波电容放在芯片同一面等,按照建议来布局布线。

去耦电容的布置尽量靠近电源管脚,且容值越小的越靠近。过孔最好打在电容的同一侧靠近。

在设计AD/DA/CLK等带模拟信号的电路时,用电源芯片将供电电源隔离,以减少干扰。其他芯片对电源有要求时同理。

FPGA

FPGA会要求大电容(Bulk Capacitor)滤掉低频、陶瓷电容滤中频,个数和数值在User Guide中有推荐,如7系列在UG483-PCB中。位置要求等也会有推荐。

Xilinx在GU1099中有BGA封装的推荐走线方式。包括宽度、距离、过孔大小等。差分线对走FPGA内部,可以选择neck mode使两线走两via之间,参数参考GU1099,注意适当选择gridless方便内部走线。

注意单端clk信号连接至FPGA的全局时钟管脚时,要连接至p端,不能连接至n端。

XILINX的FPGA的BANK分为HP/HR两种,所支持的电压、IOSTANDARD(如LVDS/LVDS_25)不同,需要注意。